# POWER MANAGEMENT IC for USB-OTG

#### **FEATURES**

- 4 Regulated Output Voltages with 3% Tolerance

- Fractional Charge Pump for 5 V/100 mA

- Fractional Charge Pump for 1.5 V/200 mA

- Doubling Charge Pump With LDO Mode for 3.3 V/22 mA

- LDO for 1.8 V/60 mA

- Switching Frequency 1 MHz

- 3 V to 5 V Operating Input Voltage Range at V<sub>CC</sub> Pin

- Sleep Mode Sets Vout2 and Vout3 Into LDO Mode

- Sleep Mode Reduces Quiescent Current of Vout2, Vout3, and Vout4 to 8 μA Each

- · internal Bus Switch

- Vbus Comparator

- Internal Soft Start Limits Inrush Current

- Low Input Current Ripple and Low EMI

- Overcurrent and Overtemperature Protected

- Undervoltage Lockout With Hysteresis

- Ultra-Small 2,5 mm x 2,7 mm Chip Scale Package Applications

## **APPLICATIONS**

- Power Supply for USB OTG for:

- Cellular Phones

- Smart Phones

- PDAs

- Handheld PCs

- Digital Cameras

- Camcorders

#### DESCRIPTION

The TPS65030 contains three charge pumps and one LDO to generate all supply voltages necessary for an USB On-The-Go (OTG) implementation using TUSB6010. The charge pumps are optimized for a single Li-Ion cell input or for 5 V from the USB bus. The input voltage range is 3 V to 5 V for the battery voltage. High efficiency is achieved by using fractional conversion techniques for the charge pumps in combination with a power saving sleep mode. The current controlled charge pumps in addition ensure low input current ripple and low EMI. Small size external ceramic capacitors are required to build a complete power supply solution. To reduce board space to a minimum, the device switches at 1-MHz operating frequency, and is available in a small 25-ball chip scale package (YZK).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION

| PACKAGED DEVICES <sup>(1)</sup> | PACKAGE    | MARKING |

|---------------------------------|------------|---------|

| TPS65030YZK                     | Chip scale | PJMI    |

(1) The YZK package is available in tape and reel. Add R suffix (TPS65030YZKR) to order quantities of 3000 parts per reel. Add T suffix (TPS65030YZKT) to order quantities of 250 parts per reel.

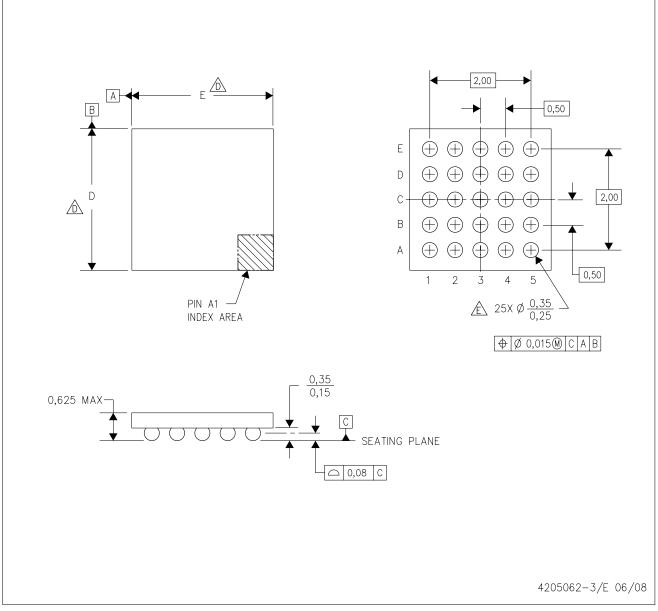

#### **PACKAGE DIMENSIONS**

| PACKAGED DEVICES (1) | D MAXIMUM | E MAXIMUM |

|----------------------|-----------|-----------|

| TPS65030YZK          | 2,708 mm  | 2,51 mm   |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                                               | VALUE         | UNIT |

|------------------|---------------------------------------------------------------|---------------|------|

| Vs               | Supply voltage at VIN, Vbus                                   | -0.3 to 7     | V    |

|                  | Voltage at EN1, EN2, EN3, SLEEP, SW_EN1, SW_EN2, PG, Test SRP | -0.3 V to VIN |      |

|                  | Output current at Vbus                                        | 200           | mA   |

|                  | Output current at Vout2                                       | 40            | mA   |

| IO               | Output current at Vout3                                       | 300           | mA   |

|                  | Output current at Vout4                                       | 100           | mA   |

| TJ               | Maximum junction temperature,                                 | 150           | °C   |

| T <sub>A</sub>   | Operating free-air temperature,                               | -40 to 85     | °C   |

| T <sub>stg</sub> | Storage temperature,                                          | -65 to 150    | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

This device contains circuits to protect its inputs and outputs against damage due to high static voltages or electrostatic fields. These circuits have been qualified to protect this device against electrostatic discharges; HBM according to EIA/JESD22-A114-B; MM according EIA/JESD22-A115-A and CDM according EIA/JESD22C101C, however, it is advised that precautions should be taken to avoid application of any voltage higher than maximum-rated voltages to these high-impedance circuits. During storage or handling, the device leads should be shorted together or the device should be placed in conductive foam. In a circuit, unused inputs should always be connected to an appropriated logic voltage level, preferably either VCC or ground. Specific guidelines for handling devices of this type are contained in the publication Guidelines for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices and Assemblies available from Texas Instruments.

# **DISSIPATION RATINGS**

| PACKAGE                  | $T_A \le 25^{\circ}C$ POWER RATING | DERATING FACTOR <sup>(1)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|--------------------------|------------------------------------|---------------------------------------------------------------|---------------------------------------|---------------------------------------|

| 25-ball chip scale (YZK) | 1.7 W                              | 17 mW/°C                                                      | 940 mW                                | 680 mW                                |

<sup>(1)</sup> The thermal resistance junction to ambient of the 5 x 5 ball chip scal package is 58°C/W when soldered on a double sided board.

# **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                                | MIN   | NOM | MAX                | UNIT |

|------------------|--------------------------------------------------------------------------------|-------|-----|--------------------|------|

| V <sub>S</sub>   | Supply voltage at VIN                                                          | 3     |     | 5                  | V    |

|                  | Maximum output current at Vbus                                                 | 100   |     |                    | mA   |

| ı                | Maximum output current at Vout2                                                | 22    |     |                    | mA   |

| 10               | Maximum output current at Vout3                                                | 200   |     |                    | mA   |

|                  | Maximum output current at Vout4                                                | 50    |     |                    | mA   |

| C <sub>I</sub>   | Input capacitor at VIN                                                         | 8     | 10  |                    | μF   |

| C 1              | Output capacitance at Vbus                                                     | 3     | 4.7 | 6.5 <sup>(1)</sup> | μF   |

| C <sub>O</sub> 1 | Output capacitance at Vbus required for stability, for $V_1 \le 4.2 \text{ V}$ | 2     |     |                    | μF   |

| C <sub>O</sub> 2 | Output capacitance at Vout2                                                    | 0.8   | 1   |                    | μF   |

| C <sub>O</sub> 3 | Output capacitance at Vout3                                                    | 8     | 10  |                    | μF   |

| C <sub>O</sub> 4 | Output capacitance at Vout4                                                    | 0.8   | 1   |                    | μF   |

|                  | Capacitance for flying capacitor, CF1A, CF1B                                   | 0.8   | 1   |                    | μF   |

|                  | Capacitance for flying capacitor CF3                                           | 0.7   | 1   |                    | μF   |

|                  | Capacitance for flying capacitor CF2                                           | 0.077 | 0.1 |                    | μF   |

| T <sub>J</sub>   | Operating junction temperature                                                 | -40   |     | 125                | °C   |

<sup>(1)</sup> Per USB spec

# **ELECTRICAL CHARACTERISTICS**

VIN = 3.6 V,  $C_I$  = 10  $\mu F$ ,  $T_A$  =  $-40^{\circ} C$  to  $85^{\circ} C$  (unless otherwise noted)

|                 | PARAMETER                                                                   | TEST CONDITIONS                                                                                       | MIN  | TYP  | MAX  | UNIT      |  |

|-----------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|-----------|--|

| SUPPL           | LY VOLTAGE AND CURRENT                                                      |                                                                                                       |      |      |      |           |  |

| V <sub>I</sub>  | Input Voltage Range, VIN                                                    |                                                                                                       | 3    |      | 5    | V         |  |

| UVLO            | Undervoltage lockout threshold                                              | Input voltage at V <sub>CC</sub> rising (device switches on)                                          | 2.91 |      | 3.0  | V         |  |

| UVLO            | Ondervoltage lockout tilleshold                                             | Input voltage at V <sub>CC</sub> falling (device switches off)                                        | 2.79 |      | 2.98 | V         |  |

|                 | Undervoltage lockout hysteresis                                             |                                                                                                       |      | 80   |      | mV        |  |

|                 | Supply current in normal mode if EN1=1, (Vbus)                              |                                                                                                       |      | 55   | 80   | μΑ        |  |

|                 | Supply current in normal mode if EN2=1, (Vout2, Vout3)                      |                                                                                                       |      | 70   | 95   | μΑ        |  |

|                 | Supply current in normal mode if EN2=EN3=1, (Vout2, Vout3, Vout4)           |                                                                                                       |      | 80   | 115  | μΑ        |  |

| I <sub>S</sub>  | Supply current in normal mode if EN1=EN2=1, (Vbus, Vout2, Vout3)            | V <sub>I</sub> = 4.2 V                                                                                |      | 110  | 145  | μΑ        |  |

| Ü               | Supply current in normal mode if EN1=EN2=EN3=1, (Vbus, Vout2, Vout3, Vout4) |                                                                                                       |      | 125  | 170  | μΑ        |  |

|                 | Supply current in sleep mode if EN2=1, (SLEEP, Vout2, Vout3)                |                                                                                                       |      | 25   | 30   | μΑ        |  |

|                 | Supply current in sleep mode if EN2=EN3=1, (SLEEP, Vout2, Vout3, Vout4)     |                                                                                                       |      | 30   | 38   | μΑ        |  |

| I <sub>SD</sub> | Shutdown current                                                            |                                                                                                       |      | 0.12 | 1    | μΑ        |  |

| CHAR            | GE PUMP STAGE FOR Vbus                                                      |                                                                                                       |      |      |      |           |  |

|                 | VBUS Output voltage                                                         |                                                                                                       |      | 5    |      | V         |  |

| Vo              | Output voltage tolerance                                                    |                                                                                                       | -4%  |      | 3%   |           |  |

| ۷O              | Output voltage ripple                                                       | $C_O 1 = 4.7 \mu F$ , $I_O 1 = 100 \text{ mA}$                                                        |      | 30   |      | $mV_{PP}$ |  |

|                 | Output voltage ripple                                                       | real cap including aging, dc bias                                                                     |      | 40   |      | шурр      |  |

|                 | Maximum output current                                                      | For Vbus > 2.5 V or $\overline{SRP}$ = high                                                           | 100  |      |      | mA        |  |

|                 | Output current limit                                                        | For Vbus $> 2.5$ V, Vbus $> V_I - 0.5$ V                                                              |      | 160  | 325  | mA        |  |

| I <sub>O</sub>  | Output current for Session Request Protocol (SRP)                           | For Vbus < 2.5 V, SRP = low                                                                           | 0.5  | 1.3  | 1.7  | mA        |  |

|                 | Output current                                                              | Vbus shorted to GND, SRP = high                                                                       |      |      | 325  | mA        |  |

|                 | Skip current limit                                                          |                                                                                                       |      | 30   |      | mA        |  |

|                 | Startup time                                                                | $C_O1 = 2 \times 4.7 \mu\text{F}, I_O = 100 \text{mA}^{(1)}, \text{ excluding}$ time for SRP $^{(2)}$ |      | 500  |      | μs        |  |

|                 | Startup time                                                                | $C_O1$ = 106 $\mu F$ , $I_O$ = 100 mA <sup>(1)</sup> , excluding time for SRP <sup>(2)</sup>          |      | 4.5  |      | ms        |  |

| f               | Switching frequency                                                         |                                                                                                       | 0.83 | 1    | 1.17 | MHz       |  |

| η               | Efficiency                                                                  | VIN = 3.6 V, I <sub>O</sub> 1 = 100 mA                                                                |      | 85%  |      |           |  |

|                 | Input current limit                                                         |                                                                                                       |      | 400  | 650  | mA        |  |

|                 | Output resistance when disabled                                             | EN1 = 0                                                                                               | 45   |      | 100  | kΩ        |  |

<sup>(1)</sup> for Vbus >2.5 V, otherwise  $I_O$  = 0 mA (2) Startup time is measured from ENx-pin going high to  $V_O$  within nominal value

# **ELECTRICAL CHARACTERISTICS (continued)**

VIN = 3.6 V,  $C_I$  = 10  $\mu F$ ,  $T_A$  =  $-40^{\circ} C$  to  $85^{\circ} C$  (unless otherwise noted)

|                    | PARAMETER                              | TEST CONDITIONS                                                                                | MIN  | TYP  | MAX  | UNIT      |

|--------------------|----------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|-----------|

| CHAR               | GE PUMP STAGE FOR Vout2                |                                                                                                |      |      |      |           |

|                    | Output voltage, Vout2                  | Normal mode                                                                                    |      | 3.3  |      | V         |

| .,                 | Output voltage tolerance               |                                                                                                | -3%  |      | 3%   |           |

| V <sub>O</sub>     | Output valle as size le                | $C_0 = 1 \mu F$ , $I_0 = 22 \text{ mA}$                                                        |      | 15   |      | >/        |

|                    | Output voltage ripple                  | real cap including aging, dc bias (0.58 μF)                                                    |      | 30   |      | $mV_PP$   |

|                    | Maximum output current                 | Normal mode                                                                                    | 22   |      |      | mA        |

| I <sub>O</sub>     | Output current limit                   | Normal mode <sup>(1)</sup>                                                                     |      | 50   | 70   | mA        |

|                    | Output voltage, Vout2                  | Sleep mode (LDO mode only)                                                                     |      | 3.3  |      | V         |

| Vo                 | Output voltage tolerance in sleep mode | $\ensuremath{\text{V}_{\text{O}}}$ drops with the battery for an input voltage less than 3.3 V | -10% |      | 4%   |           |

|                    | Maximum output current                 | Sleep mode                                                                                     | 100  |      |      | μΑ        |

|                    | Voltage drop in sleep mode             | Sleep mode, I <sub>O</sub> 2 = 100 μA                                                          |      | 25   | 150  | mV        |

|                    | Output current limit in sleep mode     | Vout2 shorted to GND                                                                           |      | 5    | 10   | mA        |

|                    | Skip current limit                     |                                                                                                |      | 5    |      | mA        |

|                    | Startup time                           | $C_0 = 1 \mu F$ , $I_0 = 22 \text{ mA}^{(2)}$                                                  |      | 200  |      | μs        |

| f                  | Switching frequency                    |                                                                                                | 0.83 | 1    | 1.17 | MHz       |

| η                  | Efficiency                             | VIN = 3.6 V, I <sub>O</sub> 2 = 22 mA , Vout2 = 3.3 V                                          |      | 90%  |      |           |

|                    | Input current limit                    | LDO mode                                                                                       |      | 50   | 70   | mA        |

|                    | Input current limit                    | Charge pump mode                                                                               |      | 100  | 140  | mA        |

| V <sub>(PG2)</sub> | Power good threshold                   | Based on the nominal output voltage (3.3 V) Vout2 increasing                                   |      | -15% |      |           |

| CHARG              | GE PUMP STAGE FOR Vout3                |                                                                                                |      |      |      |           |

|                    | Output voltage, Vout3                  | Normal mode                                                                                    |      | 1.5  |      | V         |

| $V_{O}$            | Output voltage tolerance               |                                                                                                | -3%  |      | 3%   |           |

|                    | Output voltage ripple                  | $C_0 3 = 10 \mu F$ , $I_0 3 = 200 \text{ mA}$                                                  |      | 30   |      | $mV_{PP}$ |

|                    | Maximum output current                 | Normal mode                                                                                    | 200  |      |      | mA        |

| I <sub>O</sub>     | Output current limit                   | Normal mode <sup>(3)</sup>                                                                     |      | 400  | 600  | mA        |

|                    | Output voltage                         | Sleep mode                                                                                     |      | 1.5  |      | V         |

| Vo                 | Output voltage tolerance in sleep mode |                                                                                                | -4%  |      | 4%   |           |

|                    | Maximum output current                 | Sleep mode                                                                                     | 100  |      |      | μA        |

|                    | Output current limit in sleep mode     | Vout3 shorted to GND                                                                           |      | 5    | 10   | mA        |

|                    | Skip current limit                     |                                                                                                |      | 20   |      | mA        |

|                    | Startup time                           | $C_O 3 = 10 \mu F, I_O 3 = 200 \text{ mA}^{(2)}$                                               |      | 100  |      | μs        |

| f                  | Switching frequency                    |                                                                                                | 0.83 | 1    | 1.17 | MHz       |

| η                  | Efficiency                             | VIN = 3.6 V, lout3 = 200 mA , Vout3 = 1.5 V                                                    | 1    | 80%  |      |           |

| -                  | Input current limit                    | LDO mode                                                                                       |      | 400  | 600  | mA        |

|                    | Input current limit                    | Charge pump mode                                                                               |      | 200  | 300  | mA        |

| V <sub>(PG3)</sub> | Power good threshold                   | Based on the nominal output voltage (1.5 V) Vout3 increasing                                   |      | -10% |      |           |

<sup>(1)</sup> Overload condition, current is approximately 25 mA if the output is shorted to GND.

(2) Startup time is measured from ENx-pin going high to V<sub>O</sub> within nominal value.

(3) Overload condition, current is lower if the output is shorted to GND.

# **ELECTRICAL CHARACTERISTICS (continued)**

VIN = 3.6 V,  $C_I$  = 10  $\mu F$ ,  $T_A$  =  $-40^{\circ} C$  to  $85^{\circ} C$  (unless otherwise noted)

|                    | PARAMETER                                                        | TEST CONDITIONS                                              | MIN | TYP  | MAX   | UNIT |

|--------------------|------------------------------------------------------------------|--------------------------------------------------------------|-----|------|-------|------|

| LDO FO             | OR Vout4                                                         |                                                              |     |      |       |      |

| W                  | Output voltage, Vout4                                            |                                                              |     | 1.8  |       | V    |

| Vo                 | Output voltage tolerance                                         | Normal mode                                                  | -3% |      | 3%    |      |

|                    | Maximum output current                                           | Normal mode                                                  | 60  |      |       | mA   |

| lo                 | Output current limit                                             | Normal mode                                                  |     | 110  | 160   | mA   |

|                    | Maximum output current                                           | Sleep mode                                                   | 100 |      |       | μA   |

|                    | Output voltage tolerance in sleep mode                           |                                                              | -4% |      | 4%    |      |

|                    | Current limit in sleep mode                                      | Vout4 shorted to GND                                         |     | 5    | 10    | mA   |

|                    | Startup time                                                     | $C_O 4 = 1 \mu F$ , $I_O 4 = 60 \text{ mA}^{(1)}$            |     | 100  |       | μs   |

| V <sub>(PG4)</sub> | Power good threshold                                             | Based on the nominal output voltage (1.8 V) Vout4 increasing |     | -10% |       |      |

| Vbus S             | WITCH                                                            |                                                              |     |      |       |      |

|                    | Vbus comparator turn off threshold                               | SW_ENx = 1, Vbus voltage falling                             | 4.3 |      | 4.45  | V    |

|                    | Vbus comparator hysteresis                                       |                                                              | 75  | 110  | 145   | mV   |

|                    | Turn on delay time                                               | Switching from V <sub>I</sub> to Vbus                        |     |      | 5     | μs   |

|                    | Turn off delay time                                              | Switching from Vbus to V <sub>I</sub>                        |     |      | 3     | μs   |

| V <sub>IH</sub>    | SW_EN1, SW_EN2, high level input voltage                         |                                                              | 1.2 |      |       | V    |

| V <sub>IL</sub>    | SW_EN1, SW_EN2, low level input voltage                          |                                                              |     |      | 0.3   | V    |

|                    | SW_EN1, SW_EN2 trip point hysteresis                             |                                                              |     | 50   |       | mV   |

| l <sub>ikg</sub>   | SW_EN1, SW_EN2 input resistance                                  |                                                              |     | 1    |       | MR   |

|                    | Quiescent current for Vbus comparator                            | SW_EN1 = 1 and/or SW_EN2 = 1                                 |     | 2.5  | 5     | μΑ   |

| Enable             | 1, Enable2, Enable3, Sleep, SRP                                  |                                                              |     |      |       |      |

| V <sub>IH</sub>    | EN1, EN2, EN3, Sleep, SRP high level input voltage               |                                                              | 1.2 |      |       | V    |

| V <sub>IL</sub>    | EN1, EN2, EN3, Sleep, SRP low level input voltage                |                                                              |     |      | 0.435 | V    |

|                    | EN1, EN2, EN3, Sleep, SRP trip point hysteresis                  |                                                              |     | 50   |       | mV   |

| I <sub>lkg</sub>   | EN1, EN2, Sleep, SRP input leakage current                       |                                                              |     | 0.01 | 0.2   | μΑ   |

|                    | EN3 input resistance to GND                                      |                                                              |     | 1    |       | MR   |

|                    | SLEEP exit time                                                  |                                                              |     |      | 8     | μs   |

|                    | SLEEP entry time                                                 |                                                              |     |      | 8     | μs   |

|                    | Thermal shutdown temperature                                     | Temperature rising                                           |     | 155  |       | °C   |

|                    | Thermal shutdown hysteres                                        |                                                              | 20  |      |       | °C   |

| POWER              | R GOOD                                                           |                                                              |     |      |       |      |

| V <sub>OH</sub>    | High level output voltage                                        | (open drain output)                                          |     |      | 5     | V    |

| V <sub>OL</sub>    | Low level output voltage                                         | (open drain output); Io = 1 mA                               |     |      | 0.3   | V    |

|                    | Supply voltage at VIN for power good circuit actively pulled low |                                                              | 2   |      |       | V    |

|                    | Delay time                                                       | Low to high transition                                       | 3.1 |      | 6     | ms   |

|                    | Filter time                                                      | High to low transition                                       |     | 25   |       | μs   |

<sup>(1)</sup> Startup time is measured from ENx-pin going high to  $V_{\rm O}$  within nominal value.

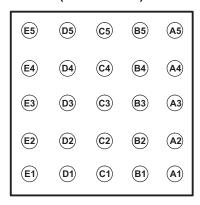

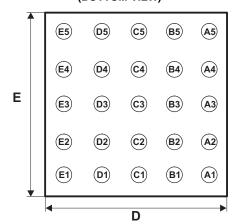

# **PIN ASSIGNMENT**

# CHIP SCALE PACKAGE (BOTTOM VIEW)

# **TERMINAL FUNCTIONS**

| TERMI  | NAL       | 1/0 | LOGIC FUNCTION                                                             | DESCRIPTION                                                                                                                                                                                                                      |  |  |

|--------|-----------|-----|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO.       | 1/0 | LOGIC FUNCTION                                                             | DESCRIPTION                                                                                                                                                                                                                      |  |  |

| EN1    | В3        | ı   | 1 = Vbus converter<br>enabled<br>0 = Vbus converter<br>disabled            | Enable input for 5-V charge pump. A logic low forces the charge pump into shutdown mode reducing the supply current to less than 1 $\mu$ A.                                                                                      |  |  |

| EN2    | B4        | ı   | 1 = Vout2 and Vout3<br>enabled<br>0 = Vout2 and Vout3<br>disabled          | Enable input for 3.3-V and 1.5-V charge pump. Logic low forces both charge pumps into shutdown mode reducing the supply current to less than 1 $\mu$ A.                                                                          |  |  |

| EN3    | C4        | I   | 1 = Vout4 enabled<br>0 = Vout4 disabled                                    | Enable input for 1.8V LDO. Logic low forces the LDO into shutdown mode reducing the supply current to less than $1\mu A$ . To ensure that EN3 is pulled to GND when left open, there is an internal pull-down resistor to GND.   |  |  |

| Vbus   | E3        | I/O | _                                                                          | Output for the 5-V charge pump. Connect the output capacitor directly to this pin. This pin is also the input for the 5-V from the USB port, if the USB port powers the 3.3-V and 1.5-V charge pump as well as the 1.8-V LDO.    |  |  |

| Vout2  | C5        | 0   | _                                                                          | Output for the 3.3-V charge pump. Connect Cout2 directly to this pin.                                                                                                                                                            |  |  |

| Vout3  | A4        | 0   | _                                                                          | Output for the 1.5-V charge pump. Connect Cout3 directly to this pin.                                                                                                                                                            |  |  |

| Vout4  | E4        | 0   | _                                                                          | Output for the 1.8-V LDO. Connect Cout4 directly to this pin.                                                                                                                                                                    |  |  |

| SLEEP  | B2        | ı   | 1 = sleep mode<br>0 = normal mode                                          | This pin is used to set the 3.3-V and 1.5-V charge pump as well as the 1.8-V LDO into sleep mode. Logic low forces the charge pumps into normal operating mode if they are enabled.                                              |  |  |

| PGood  | D3        | 0   | 1 = output voltage within limits 0 = output voltage too low                | Open drain power good output for Vout2,Vout3, and Vout4                                                                                                                                                                          |  |  |

| SW_EN1 | С3        | ı   | 1 = Vout3 switchover to<br>Vbus enabled<br>0 = Vout3 is battery<br>powered | Enable input 1 for internal USB switch. If this input is pulled high, the Vout3 converter is powered from Vbus. If SLEEP is pulled high, the converter is always powered from the battery, independent from the state of SW_EN1. |  |  |

| SW_EN2 | C2        | ı   | 1 = Vout2 switchover to<br>Vbus enabled<br>0 = Vout2 is battery<br>powered | Enable input 2 for internal USB switch. If this input is pulled high, the Vout2 converter is powered from Vbus. If SLEEP is pulled high, the converter is always powered from the battery, independent from the state of SW_EN2. |  |  |

| VIN    | A1,<br>A2 | I   | _                                                                          | Supply voltage input                                                                                                                                                                                                             |  |  |

| CF1A+  | C1        |     |                                                                            | Connect to the flying capacitor CF1A                                                                                                                                                                                             |  |  |

| CF1A-  | E1        |     |                                                                            | Connect to the flying capacitor CF1A                                                                                                                                                                                             |  |  |

| CF1B+  | B1        | _   | _                                                                          | Connect to the flying capacitor CF1B                                                                                                                                                                                             |  |  |

| CF1B-  | D1        | _   | _                                                                          | Connect to the flying capacitor CF1B                                                                                                                                                                                             |  |  |

| CF2+   | D5        | _   | _                                                                          | Connect to the flying capacitor CF2                                                                                                                                                                                              |  |  |

# **TERMINAL FUNCTIONS (continued)**

| TERMIN   | IAL       | 1/0 | LOGIC FUNCTION                                                   | DESCRIPTION                                                                                                                                                                                                                             |  |

|----------|-----------|-----|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO.       | I/O | LOGIC FUNCTION                                                   | DESCRIPTION                                                                                                                                                                                                                             |  |

| CF2-     | E5        | _   | _                                                                | Connect to the flying capacitor CF2                                                                                                                                                                                                     |  |

| CF3+     | А3        | _   | _                                                                | Connect to the flying capacitor CF3                                                                                                                                                                                                     |  |

| CF3-     | A5        | _   | _                                                                | Connect to the flying capacitor CF3                                                                                                                                                                                                     |  |

| Test SRP | D2        | I/O | Input:<br>$1 = I_O$ at Vbus = 100 mA<br>$0 = I_O$ at Vbus = 1 mA | Open drain output for connectivity test, input for current limit during startup for Vbus voltage if the device is not in test mode. If Test SRP is pulled high, the Vbus current during startup is > 100 mA. If pulled low, it is 1 mA. |  |

| PGND     | E2,<br>B5 | _   | _                                                                | Power ground                                                                                                                                                                                                                            |  |

| GND      | D4        | _   | _                                                                | Analog Ground                                                                                                                                                                                                                           |  |

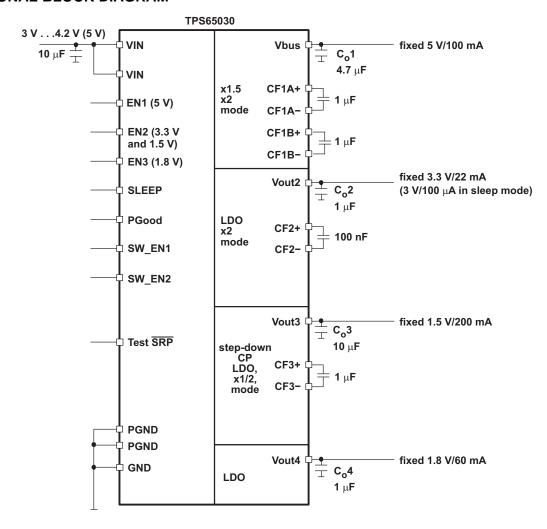

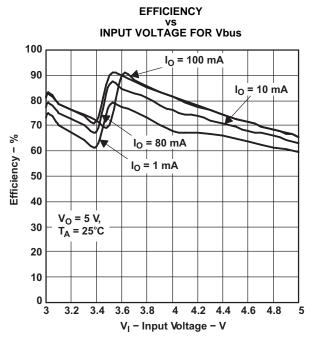

#### **FUNCTIONAL BLOCK DIAGRAM**

# **INTERNAL BLOCK DIAGRAM**

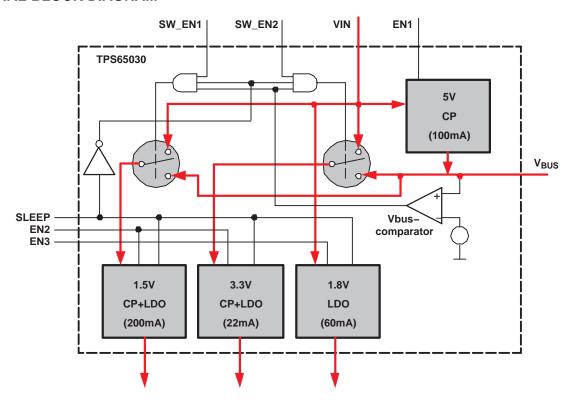

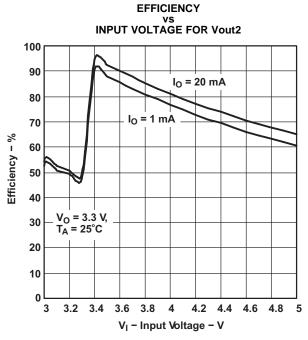

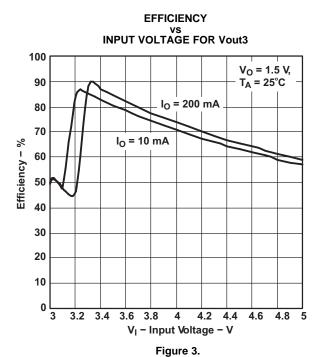

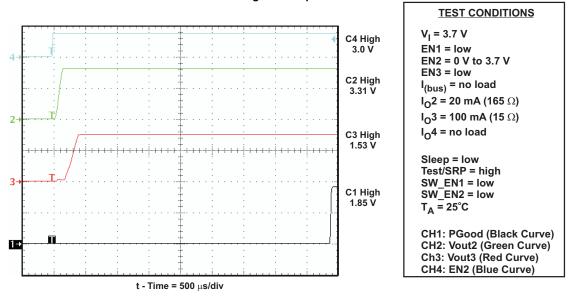

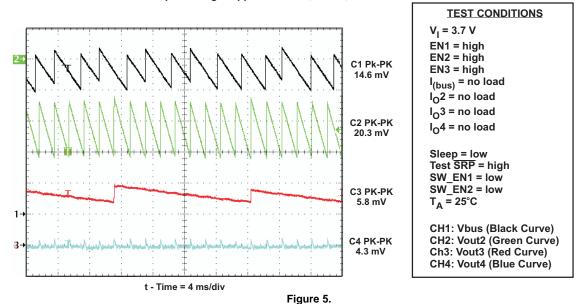

# **TYPICAL CHARACTERISTICS**

# **Table of Graphs**

|   |                                                                |                                                                                                                      | FIGURE |

|---|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------|

| η |                                                                | vs input voltage at Vbus                                                                                             | 1      |

|   | Efficiency                                                     | vs input voltage at Vout2                                                                                            | 2      |

|   |                                                                | vs input voltage at Vout3                                                                                            | 3      |

|   | Power good timing at startup of Vout2 and Vout3                | $V_1 = 3.7 \text{ V}; I_0 = 20 \text{ mA}; I_0 = 100 \text{ mA}$                                                     | 4      |

|   | Output voltage ripple Vout2, Vout3, Vout4 at no load           | V <sub>I</sub> = 3.7 V; no load                                                                                      | 5      |

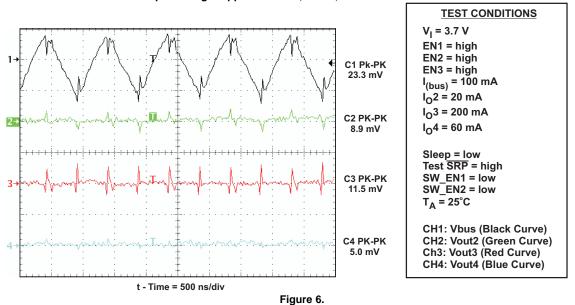

|   | Output voltage ripple Vout2, Vout3, Vout4 at full load         | $V_1 = 3.7 \text{ V}; I_{(bus)} = 100 \text{ mA}; I_0 = 20 \text{ mA}; I_0 = 100 \text{ mA}, I_0 = 60 \text{mA}$     | 6      |

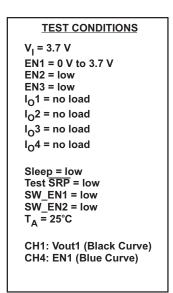

|   | Vbus startup with SRP = 0                                      | No load                                                                                                              | 7      |

|   | Vbus startup with SRP = 1                                      | 50-mA load                                                                                                           | 8      |

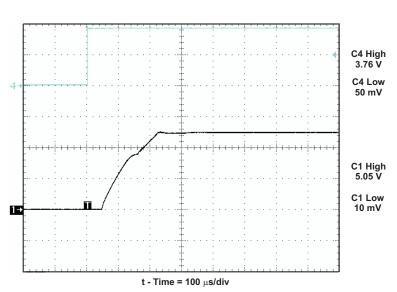

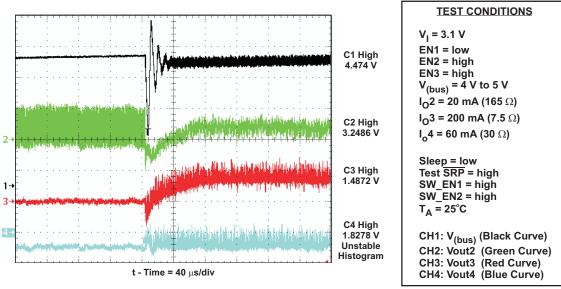

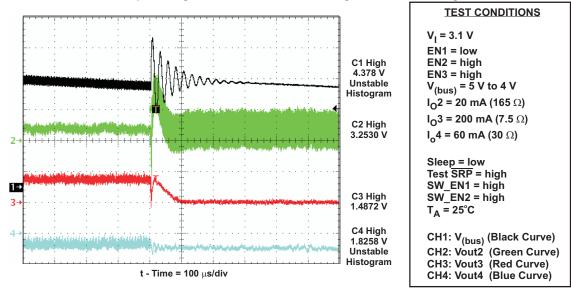

|   | Output voltage of Vout2,Vout3, and Vout4 during Vbus switching | $V_1 = 3.1 \text{ V}; I_0 = 20 \text{ mA}; I_0 = 100 \text{ mA}, I_0 = 60 \text{ mA}$                                | 9      |

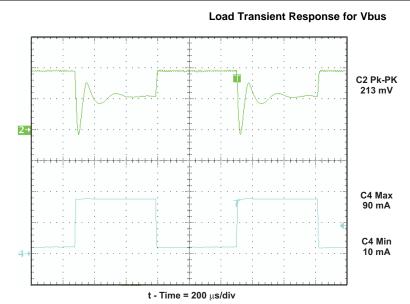

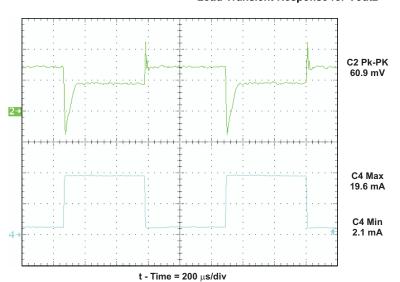

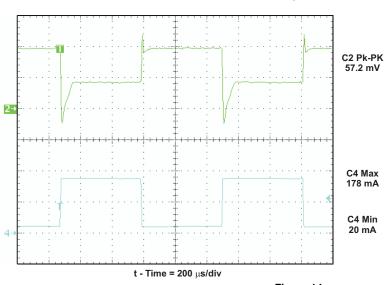

|   | Load transient response of Vbus                                | $V_I = 3.1 V$ and $V_I = 3.7 V$ , $I_{(bus)} = 10$ mA to 90 mA to 10 mA                                              | 10     |

|   | Load transient response of Vout2                               | $V_1 = 3.1V$ , $V_1 = 3.7$ V, Vbus = 5 V, $I_0 = 2$ mA to 20 mA to 2 mA                                              | 11     |

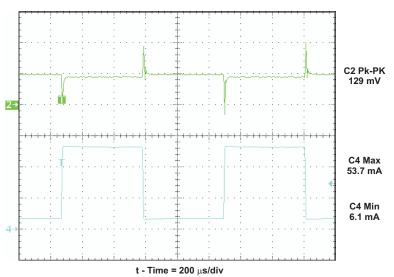

|   | Load transient response of Vout3                               | $V_I = 3.1 \text{V}, V_I = 3.7 \text{ V}, \text{Vbus=5 V}, I_O = 20 \text{ mA to } 180 \text{ mA to } 20 \text{ mA}$ | 12     |

|   | Load transient response of Vout4                               | $V_{I} = 3.1V$ , $V_{I} = 3.7$ V, Vbus=5 V, $I_{(bus)} = 10$ mA to 90 mA to 1 0mA                                    | 13     |

Figure 1.

Figure 2.

Figure 4.

#### Output Voltage Ripple for Vout2, Vout3, Vout4 at no Load

#### Output Voltage Ripple for Vout2, Vout3, Vout4 at Full Load

#### Vbus Startup With $\overline{SRP} = 0$

Figure 7.

TEST CONDITIONS  $V_I = 3.7 \text{ V}$ EN1 = 0 V to 3.7 V

EN2 = low

EN3 = low  $I_{O}1 = 50 \text{ mA}$   $I_{O}2 = \text{no load}$   $I_{O}3 = \text{no load}$   $I_{O}4 = \text{no load}$ Sleep = low

Test  $\overline{SRP} = \text{high}$ SW\_EN1 = low

SW\_EN2 = low  $T_A = 25^{\circ}\text{C}$

CH1: Vout1 (Black Curve) CH4: EN1 (Blue Curve)

Figure 8.

# Output Voltage Ripple for Vout2, Vout3, Vout4 During Vbus Switching

Figure 9.

| Switching                                                                                                |

|----------------------------------------------------------------------------------------------------------|

| <b>TEST CONDITIONS</b>                                                                                   |

| V <sub>I</sub> = 3.1 V                                                                                   |

| EN1 = low                                                                                                |

| EN2 = high                                                                                               |

| EN3 = high                                                                                               |

| Vbus = 4 V to 5 V to 4 V                                                                                 |

| $I_{O}^{2} = 20 \text{ mA } (165 \Omega)$                                                                |

| $I_{O}^{3} = 200 \text{ mA } (7.5 \Omega)$                                                               |

| $I_0 4 = 60 \text{ mA } (30 \Omega)$                                                                     |

| Sleep = low<br>Test SRP = high<br>SW_EN1 = high<br>SW_EN2 = high<br>T <sub>A</sub> = 25°C                |

| CH1: Vbus (Black Curve)<br>CH2: Vout2 (Green Curve)<br>CH3: Vout3 (Red Curve)<br>CH4: Vout4 (Blue Curve) |

#### Output Voltage of Vout2, Vout3, Vout4 During V<sub>I</sub> to Vbus Switching

Figure 10.

#### Output Voltage of Vout2, Vout3, Vout4 During Vbus to VI Switching

Figure 11.

#### Figure 12.

# TEST CONDITIONS $V_1 = 3.1 \text{ V}$ EN1 = high EN2 = low EN3 = low $I_{\text{(bus)}} = 10 \text{ mA to } 90 \text{ mA}$ $I_{\text{O}} = \text{no load}$ $I_{\text{O}} = \text{no load}$ $I_{\text{O}} = \text{no load}$ Sleep = low Test $\overline{\text{SRP}} = \text{high}$ SW\_EN1 = low SW\_EN2 = low $T_{\text{A}} = 25^{\circ}\text{C}$ CH2: Vout1 (Green Curve) CH4: I\_{\text{O}} (Blue Curve)

#### **Load Transient Response for Vout2**

Figure 13.

# TEST CONDITIONS $V_I = 3.1 \text{ V}$ EN1 = low EN2 = high EN3 = low $I_{(bus)} = \text{no load}$ $I_{O}2 = 2 \text{ mA to } 20 \text{ mA}$ $I_{O}3 = \text{no load}$ $I_{O}4 = \text{no load}$ Sleep = low Test $\overline{\text{SRP}} = \text{high}$ SW\_EN1 = low SW\_EN2 = low $T_A = 25^{\circ}\text{C}$ CH2: Vout2 (Green Curve) CH4: $I_{O}2$ (Blue Curve)

# **TEST CONDITIONS**

V<sub>I</sub> = 3.1 V EN1 = low EN2 = high EN3 = low Vbus = no load Vout2 = no load Vout3 = 20 mA to 180 mA Vout4 = no load

Sleep = low Test SRP = high SW\_EN1 = low SW\_EN2 = low T<sub>A</sub> = 25°C

CH2: Vout3 (Green Curve) CH4: I<sub>O</sub>3 (Blue Curve)

Figure 14.

#### **Load Transient Response for Vout4**

Figure 15.

#### **TEST CONDITIONS**

V<sub>1</sub> = 3.1 V EN1 = low EN2 = low EN3 = high I<sub>(bus)</sub> = no load I<sub>O</sub>2 = no load I<sub>O</sub>3 = no load I<sub>O</sub>4 = 6 mA to 54 mA

Sleep = low Test SRP = high SW\_EN1 = low SW\_EN2 = low T<sub>A</sub> = 25°C

CH2: Vout4 (Green Curve) CH4: I<sub>O</sub>4 (Blue Curve)

#### **DETAILED DESCRIPTION**

# Operation

The TPS65030 uses fractional conversion charge pumps to generate the supply voltage for an integrated USB OTG chip (TUSB6010). Depending on the input voltage, output voltage, and output current, the charge pumps operate in different conversion modes. By switching automatically between these different modes the circuit optimizes the power conversion efficiency as well as extends operating.

## **Operating Modes**

The TPS65030 contains three charge pumps and one LDO. The charge pumps for Vout2 and Vout3 as well as the LDO, used to generate Vout4, can either operate in normal mode or in sleep mode. See the *SLEEP* paragraph for details.

The charge pumps operate in the LinSkip mode. This mode allows to switch seamlessly from the power saving pulse skip mode at light loads, to the low-noise, constant frequency linear-regulation mode, once the output current exceeds the device-specific output current threshold. This output current at which the device switches between these two operating modes is called skip current limit. In order to provide a good efficiency over a wide load range, the skip current limit is set to approximately 25% of the nominal output current for each converter. If the output current drops below the skip current threshold, the device begins to skip switching cycles which reduces its switching frequency and associated switching losses.

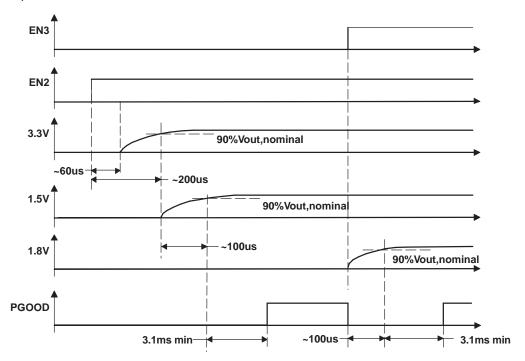

# Enable (EN1, EN2, EN3)

There are 3 different enable signals available. EN1 activates the 5-V converter associated with Vbus if it is pulled high. EN2 is associated with the 3.3-V converter (Vout2) and the 1.5-V converter (Vout3). If EN2 is pulled high, the 3.3-V ramps up first, followed by the 1.5-V converter, see Figure 16. EN3 enables the 1.8-V LDO (Vout4) if pulled high. For EN3, there is an internal pull-down resistor to GND, disabling the Vout4-LDO if the EN3 pin is left open.

Figure 16. Timing Diagram

# **DETAILED DESCRIPTION (continued)**

#### **Soft Start**

The TPS65030 has an internal soft start circuit that limits the inrush current during start-up. This prevents possible voltage drops of the input voltage if a high impedance power source is connected to the input of the TPS65030. The input current for each converter is limited to about twice the nominal input current in normal operating.

## Switch\_Enable (SW\_EN1, SW\_EN2)

The enable pins SW\_EN1 and SW\_EN2 are used to activate an internal switch that connects the input for the 3.3-V charge pump and the input of the 1.5-V charge pump with either the Li-ion battery or the USB bus voltage of 5 V. SW\_EN1 controls the bus switch for Vout3 (1.5 V), while SW\_EN2 controls the bus switch for Vout2 (3.3 V). Vout1 and Vout4 are always battery powered. Both inputs are active high. The turnover from V<sub>I</sub> to Vbus is handled in such a way that the SW\_ENx signals are used as an enable signal to the bus switch. Switchover, however, occurs based on the status of the Vbus comparator. The Vbus comparator senses the voltage at Vbus. If the voltage is above the threshold, the power source for the converters, enabled by SW\_ENx is switched from the battery to the USB bus voltage. If the voltage at Vbus drops below the threshold, the power source is switched back to the battery again. The internal Vbus comparator is disabled if both SW\_EN1 and SW\_EN2 are low, to reduce the quiescent current of the device.

#### Sleep

The TPS65030 offers a power save mode (sleep mode), that reduces the maximum output current of the converters for Vout2, Vout3 and Vout4. The Maximum output current for each converter is reduced to 100  $\mu$ A. In sleep mode, the quiescent supply current for each converter is reduced to 8  $\mu$ A maximum. Sleep mode is entered when the sleep pin is pulled high. In sleep mode, all converters are switched to battery power, independent from the state of SW\_EN1 and SW\_EN2. In sleep mode, the charge pumps stop operation, and a separate 100- $\mu$ A LDO in each converter supplies the output voltage.

#### **Power Good**

The power good signal is provided by an open drain output. The status of this pin depends on the status of the power good comparators for Vout2, Vout3 and Vout4. Only the converters that are enabled determine the status of the power good signal. If the output voltage of all converter that are enabled, is within its limits, the power good signal goes high. The open drain output is pulled high using an external resistor to 5.5-V maximum. If all converters are disabled, power good is held low. There is a power good delay of 3.1ms minimum after the voltage of all power rails that are enabled rose above their power good threshold.

#### **Undervoltage Lockout**

The undervoltage lockout circuit shuts down the device when the voltage on VIN drops below a typical threshold of 2.9 V. This prevents the device and application from damage. The UVLO circuit allows the device to start up again after the voltage on the VIN pin increased by about 80 mV.

# **Short Circuit and Overtemperature Protection**

The current at the different outputs are limited. When the junction temperature exceeds 155°C, the device shuts down to protect the device from damage. After the temperature decreased to about 135°C, the device starts up if it is still enabled. In order to reduce the quiescent current, the overtemperature protection is disabled in sleep-mode.

#### **TEST Input SRP Enable**

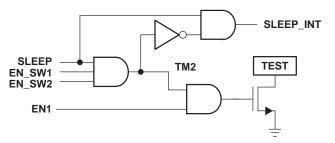

The TEST input  $\overline{\sf SRP}$  enable pin has two functions. It is an output when the device is in test mode or an input in normal mode.

In order to test the electrical connections between the power supply chip (TPS65030) and the USB-OTG

## **DETAILED DESCRIPTION (continued)**

transceiver (TUSB6010), a test mode is available on TPS65030. The TEST pin is used as an output to TUSB6010. This test mode is entered when EN\_SW1 and EN\_SW2 and SLEEP are high at the same time. In this case the actual function of SLEEP is disabled and the output pin TEST is changed from high-impedance state to low in case that EN1=1. For all other conditions of EN\_SW1, EN\_SW2, SLEEP, and EN1 it stays in high impedance state, see Table 1.

The test mode should be entered with the following sequence:

- set SLEEP = 0

- set EN1 = 0

- make sure Vbus is not supplied from external source (Vbus < 4.3 V)</li>

- set SW\_EN1 = SW\_EN2 = 1

- set SLEEP = 1 (this enters the test mode)

- toggle EN1 to switch between low and high impedance on TEST output pin

| EN_SW1 | EN_SW2 | SLEEP | EN1 | TEST           |

|--------|--------|-------|-----|----------------|

| 0      | 0      | 0     | 0   | High impedance |

| 0      | 0      | 0     | 1   | High impedance |

| 0      | 0      | 1     | 0   | High impedance |

| 0      | 0      | 1     | 1   | High impedance |

| 0      | 1      | 0     | 0   | High impedance |

| 0      | 1      | 0     | 1   | High impedance |

| 0      | 1      | 1     | 0   | High impedance |

| 0      | 1      | 1     | 1   | High impedance |

| 1      | 0      | 0     | 0   | High impedance |

| 1      | 0      | 0     | 1   | High impedance |

| 1      | 0      | 1     | 0   | High impedance |

| 1      | 0      | 1     | 1   | High impedance |

| 1      | 1      | 0     | 0   | High impedance |

| 1      | 1      | 0     | 1   | High impedance |

| 1      | 1      | 1     | 0   | High impedance |

| 1      | 1      | 1     | 1   | 0              |

**Table 1. Interconnection Test Mode**

The principle is also shown in Figure 17.

Figure 17.

When the device is in normal mode (not in test mode), the pin is used as an input to enable or disable the SRP feature of the Vbus charge pump. If the TEST  $\overline{\sf SRP}$  pin is held low, the SRP feature is enabled and the charge pump starts up with a current limit of 1 mA until the voltage at Vbus reaches 2.5 V. If the voltage exceeds 2.5 V, the current limit is increased to a higher value in order to provide 100 mA of output current. If  $\overline{\sf SRP}$  is pulled high, the charge pump starts with a higher current limit even for Vbus < 2.5 V in order to provide enough output current to start into a 100 mA load.

# Theory or Operation / Design Procedure

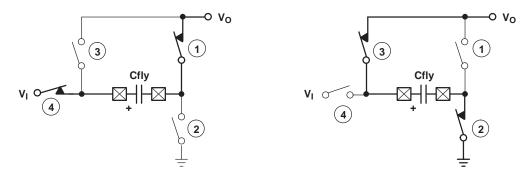

# Charge Pump Operation (Based on Vout3 Step-Down Converter)

The description of how the charge pumps operate is based on the design of the step-down charge pump used for Vout3. This converter either operates in a LDO mode for input voltages (battery voltage) lower than 3.5 V. If the input voltage exceeds 3.5 V, the converter operates as a step-down charge pump. As the efficiency of a charge pump mainly depends on the input, output voltage ratio and its operating mode (LDO or  $\times 1/2$ ), the efficiency graph shows a typical sawtooth waveform. This is caused by the fact that the charge pump can only increase efficiency if it switches to a different operating mode but not by adjusting its duty cycle like in inductive converters, where the efficiency curve is smooth

#### **LDO Conversion Mode**

In the LDO mode the flying capacitor is not used for transferring energy. The switches 3 and 4 are closed and connect the input directly with the output. This mode is automatically selected if the input voltage is too low to provide enough output voltage in x1/2 charge pump mode. In LDO mode the regulation is done by regulating the current through switch 4. For an output current of less than 20 mA, the current through switch is turned on and off like in SKIP mode regulation.

#### X1/2 Conversion Mode

This conversion mode is internally selected if the input to output voltage ratio is greater than 2. In the first switching cycle, the flying capacitor is charged in series with the output capacitor. In the second cycle the flying capacitor is connected in parallel with the output capacitor which discharges the flying capacitor and charges the output. Regulation is done similar to LDO mode by regulating the current through switch 4. For an output current less than the SKIP current threshold, switch 4 does not turn on each switching cycle unless energy is needed at the output. The device now operates in skip mode with a lower switching frequency, depending on the load current.

#### **X2 Conversion Mode**

This conversion mode applies to the converter used to generate Vout2. It is used to generate an output voltage that is higher than the input voltage. In the first switching cycle, the flying capacitor is charged in parallel to the input voltage. In the second switching cycle, the flying capacitor is connected in series with the input voltage, charging the output capacitor to twice the input voltage. Regulation of the output voltage is done similar to the other conversion modes.

#### Sleep-Mode LDO

In sleep mode, a separate LDO in the charge pump block, supplied from the battery, is used to provide the output voltage.

# Theory or Operation / Design Procedure (continued)

#### **Capacitor Selection**

Ceramic capacitors such as X5R or X7R are recommended to be used with TPS65030. Low ESR capacitors on VOUTx reduce the ripple voltage on the output of the supplies. Table 2 lists capacitor types that have been tested with the TPS65030. For the flying capacitors, the value is not critical. For values lower than those listed in the recommended table, the performance of the converter decreases with regard to maximum output current at minimum input voltage. It also causes the converter to switch to its lower efficient mode at a higher input voltage. The value of the output capacitors is critical for stability. A high dc-bias voltage at ceramic capacitors causes a lower capacitance than expected. This effect is critical for Vbus with an output voltage of 5 V. The Vbus converter is designed to operate with a minimum capacitance of 3  $\mu$ F. In order to keep the minimum capacitance at Vbus above 3  $\mu$ F, a voltage rating for Cout1 of more than 6.3 V may be required, depending on the specification given by its manufacturer.

**Table 2. Capacitors**

| PART           | VALUE  | VOLTAGE | MANUFACTURER | SIZE | NOTES    |

|----------------|--------|---------|--------------|------|----------|

| C1005X5R1A104K | 100 nF | 10 V    | TDK          | 0402 |          |

| C1608X5R1A105M | 1 μF   | 10 V    | TDK          | 0603 |          |

| C2012X5R1A475M | 4.7 µF | 10 V    | TDK          | 0805 | For Vbus |

| C2012X5R0J106M | 10 μF  | 6.3 V   | TDK          | 0805 |          |

The voltage rating on the flying capacitors is given in Table 3.

**Table 3. Voltage Ratings**

| REFERENCE  | ERENCE VALUE VOLTAGE ACROSS FLYING CAPACITOR |       |       |

|------------|----------------------------------------------|-------|-------|

| CF1A, CF1B | 1 μF                                         | VIN   | 6.3 V |

| CF2        | 100 nF                                       | Vout2 | 4 V   |

| CF3        | 1 μF                                         | Vout3 | 4 V   |

Due to aging and dc bias effect, the minimum value of real capacitors when these are minimum size, may be lower than the initial design goals for TPS65030. Therefore TPS65030 has been verified by simulations to be fully functional and stable with the worst case values for the capacitors given in the table below. Due to the low capacitance, the output ripple voltage and transient voltage have a different value compared to the capacitors listed in RECOMMENDED OPERATING CONDITIONS. These values are additionally given in the electrical characteristics.

# Minimum capacitor value for operation

|                  |                                                                                                               | MIN   | NOM | MAX | UNIT |

|------------------|---------------------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| C <sub>I</sub>   | Input capacitance                                                                                             | 8     |     |     | μF   |

| C <sub>O</sub> 1 | Output capacitance at Vbus; for $V_1 \le 4.2 \text{ V}$                                                       | 2     |     |     | μF   |

| C <sub>O</sub> 2 | Output capacitance at Vout2                                                                                   | 0.58  |     |     | μF   |

| C <sub>O</sub> 3 | Output capacitance at Vout3                                                                                   | 8     |     |     | μF   |

| C <sub>O</sub> 4 | Output capacitance at Vout4                                                                                   | 0.8   |     |     | μF   |

|                  | Capacitance for flying capacitor, CF1A, CF1B, $\rm V_{I}$ min > 3.05 V to support an output current of 100 mA | 0.52  |     |     | μF   |

|                  | Capacitance for flying capacitor CF3                                                                          | 0.7   |     |     | μF   |

|                  | Capacitance for flying capacitor CF2                                                                          | 0.077 |     |     | μF   |

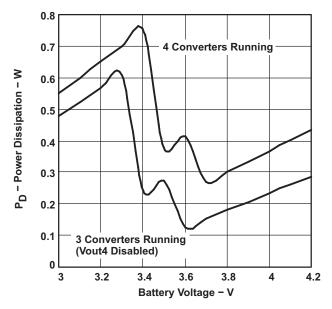

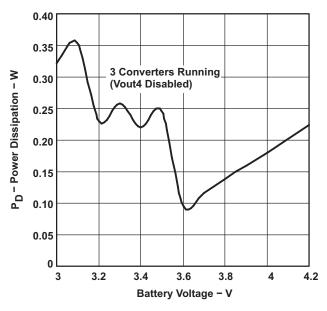

#### **Power Dissipation**

In normal operation when the battery voltage is at its nominal value of 3.8 V, the TPS65030 has very low power dissipation as it is optimized for operation with one Li-ion cell. If all outputs are fully loaded, the internal power dissipation is about 300 mW at  $V_1 = 3.8$  V. The measurements were taken with decreasing battery voltage similar to a real battery powered system.

Figure 18. Power Dissipation vs Battery Voltage

Typically, the TUSB6010 requires less than the full supply current specified for the TPS65030. Figure 19 shows the power dissipation with the typical current required by TUSB6010. Vbus is loaded with 100 mA, Vout2 is loaded with 20 mA and Vout3 is loaded with 100 mA.

Figure 19. Power Dissipation vs Battery Voltage

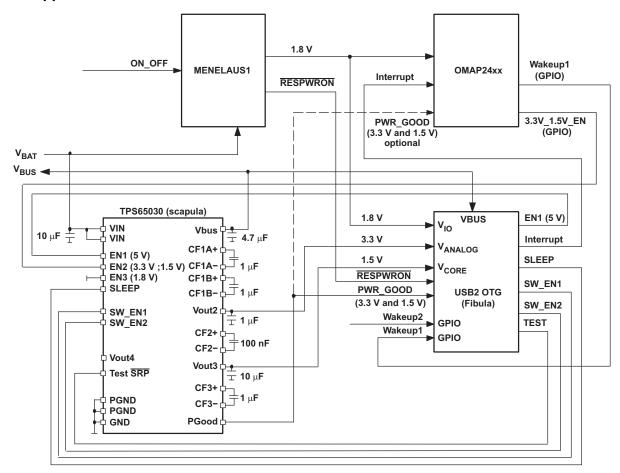

# **APPLICATION INFORMATION**

# **Typical Application**

## **APPLICATION INFORMATION (continued)**

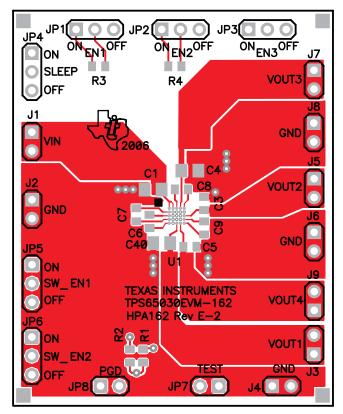

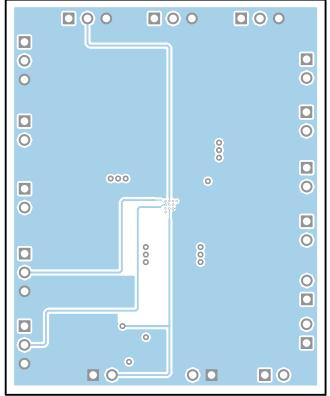

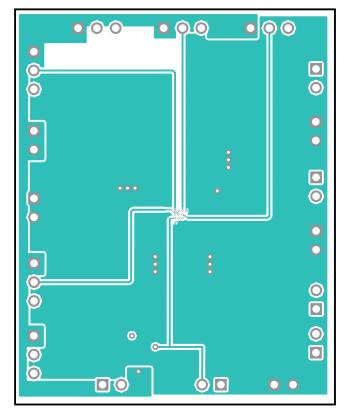

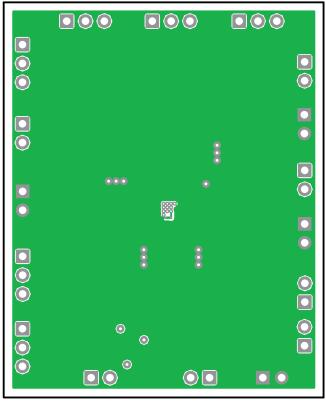

# **Layout and Board Space**

All capacitors should be soldered as close as possible to the IC. A PCB layout proposal for a four-layer board is shown in Figure 20 to Figure 23. Care has been taken to connect all capacitors as close as possible to the circuit to achieve optimized output voltage ripple performance. All critical connections like power input / output pins and the pins for the flying capacitors are located on the outside of the package. Signal connections like enable signals are located in the inside and can be routed on the bottom layer or on a signal layer. Power connections should be routed on the layer, the device is placed. A GND plane should be used for optimal performance of the device.

Figure 20. EVM Top Layer

Figure 21. EVM Layer 2

# **APPLICATION INFORMATION (continued)**

Figure 22. EVM Layer 3

Figure 23. EVM Bottom Layer

#### **EVM WARNINGS AND RESTRICTIONS**

It is important to operate this EVM within the input voltage range of 3 V to 5 V and the output voltage range of 1.5 V to 5 V.

Exceeding the specified input range may cause unexpected operation and/or irreversible damage to the EVM. If there are questions concerning the input range, please contact a TI field representative prior to connecting the input power.

Applying loads outside of the specified output range may result in unintended operation and/or possible permanent damage to the EVM. Please consult the EVM User's Guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative.

During normal operation, some circuit components may have case temperatures greater than 50C. The EVM is designed to operate properly with certain components above 50C as long as the input and output ranges are maintained. These components include but are not limited to linear regulators, switching transistors, pass transistors, and current sense resistors. These types of devices can be identified using the EVM schematic located in the EVM User's Guide. When placing measurement probes near these devices during operation, please be aware that these devices may be very warm to the touch.

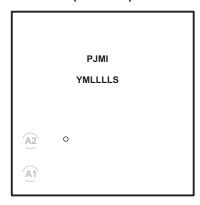

# **PACKAGE SUMMARY**

# CHIP SCALE PACKAGE (BOTTOM VIEW)

# CHIP SCALE PACKAGE MARKINGS (TOP VIEW)

#### Code:

- PJMI identifies the chip as TPS65030

- Y year

- M month

- L lot trace code

- S site code

# **PACKAGE DIMENSIONS**

The dimensions for the YZK package are shown in Table 4. See the package drawing at the end of this data sheet.

**Table 4. YZK Package Dimensions**

| Packaged Devices | D Maximum | E Maximum |

|------------------|-----------|-----------|

| TPS65030YZK      | 2,708 mm  | 2,51 mm   |

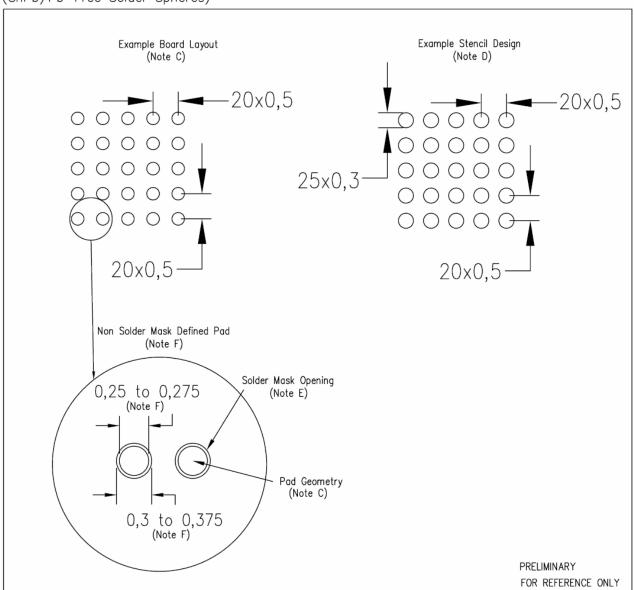

# YEK/YZK (S-XBGA-N25)

(SnPb/Pb-Free Solder Spheres)

#### NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-SM-782 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

- F. Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints. Refer to Wafer Chip Scale Packages, Texas Instruments Literature No. SBVA017 and also the Product Data Sheet for specific thermal information via requirements, and recommended routing guidelines. These documents are available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

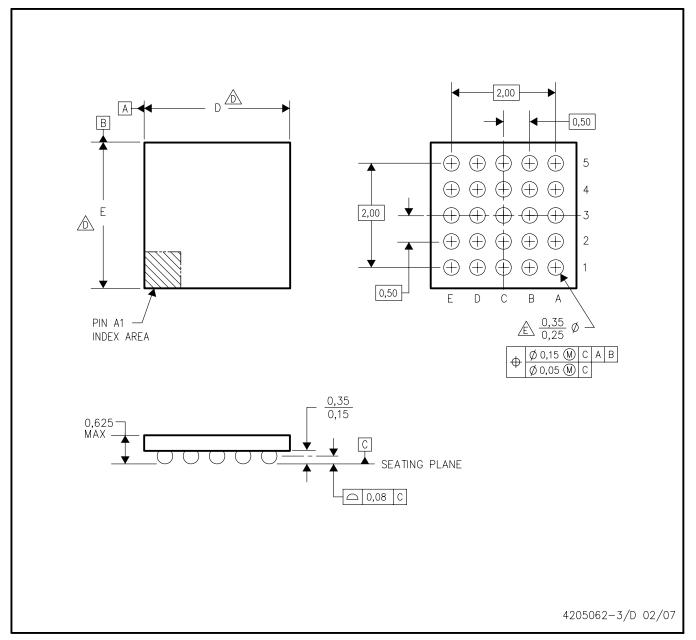

# YZK (S-XBGA-N25)

# DIE-SIZE BALL GRID ARRAY

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. NanoFree™ package configuration.

- Devices in YZK package can have dimension D ranging from 2.35 to 3.15 mm and dimension E ranging from 2.35 to 3.15 mm.

To determine the exact package size of a particular device, refer to the device datasheet or contact a local TI representative.

- E Reference Product Data Sheet for array population. 5 x 5 matrix pattern is shown for illustration only.

- F. This package contains lead—free balls. Refer to YEK (Drawing #4204185) for tin—lead (SnPb) balls.

#### PACKAGE OPTION ADDENDUM

www.ti.com 16-Apr-2009

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins F | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|--------|----------------|---------------------------|------------------|------------------------------|

| TPS65030YZKR     | ACTIVE                | DSBGA           | YZK                | 25     | 3000           | Green (RoHS & no Sb/Br)   | SNAGCU           | Level-1-260C-UNLIM           |

| TPS65030YZKT     | ACTIVE                | DSBGA           | YZK                | 25     | 250            | Green (RoHS & no Sb/Br)   | SNAGCU           | Level-1-260C-UNLIM           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND**: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

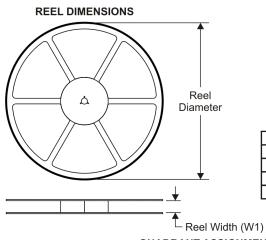

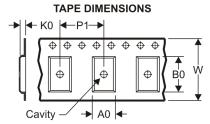

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

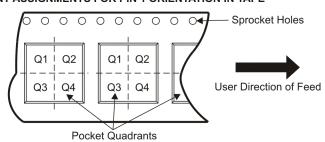

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TPS65030YZKR | DSBGA           | YZK                | 25 | 3000 | 180.0                    | 8.4                      | 2.6     | 2.8     | 0.81    | 4.0        | 8.0       | Q1               |

| TPS65030YZKT | DSBGA           | YZK                | 25 | 250  | 180.0                    | 8.4                      | 2.6     | 2.8     | 0.81    | 4.0        | 8.0       | Q1               |

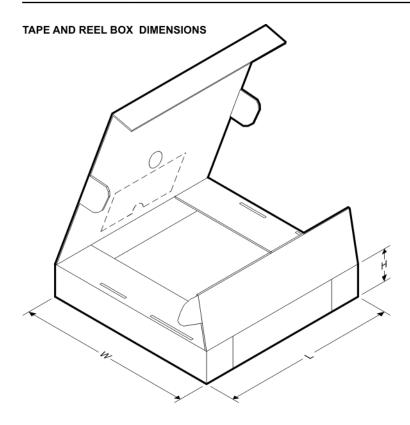

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS65030YZKR | DSBGA        | YZK             | 25   | 3000 | 220.0       | 220.0      | 34.0        |

| TPS65030YZKT | DSBGA        | YZK             | 25   | 250  | 220.0       | 220.0      | 34.0        |

# YZK (S-XBGA-N25)

# DIE-SIZE BALL GRID ARRAY

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. NanoFree™ package configuration.

- Devices in YZK package can have dimension D ranging from 2.44 to 3.15 mm and dimension E ranging from 2.44 to 3.15 mm.

To determine the exact package size of a particular device, refer to the device datasheet or contact a local TI representative.

- E. Reference Product Data Sheet for array population. 5 x 5 matrix pattern is shown for illustration only.

- F. This package contains lead—free balls. Refer to YEK (Drawing #4204185) for tin—lead (SnPb) balls.

NanoFree is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions